# AMATH 483/583 High Performance Scientific Computing

# Lecture 6: High Performance in Hierarchical Memory

Andrew Lumsdaine

Northwest Institute for Advanced Computing

Pacific Northwest National Laboratory

University of Washington

Seattle, WA

#### **Overview**

- "PDP-11" machine model

- Pipelining, pipeline stalls

- Hierarchical memory

- Timing and benchmarking

- Compiler optimizations

- Tiling

- Blocking

#### **Microprocessors**

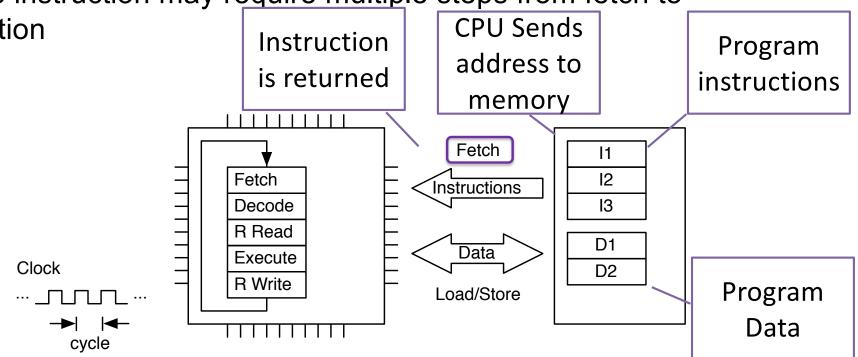

Basic operation: read and execute program instructions stored in memory

Fundamental performance / efficiency metric: cycles per instruction (CPI) also FL( Instructions can only be Fetch run in CPU Instructions **Transitions CPU** Memory Clock move data Data through CPU Program Load/Store cycle Data can only instructions be operated and data on in CPU NORTHWEST INSTITUTE for ADVANCED CUMPUTING

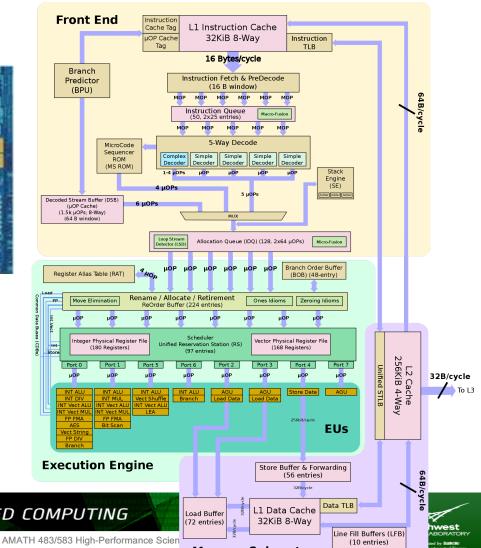

#### **Performance-Oriented Architecture Features**

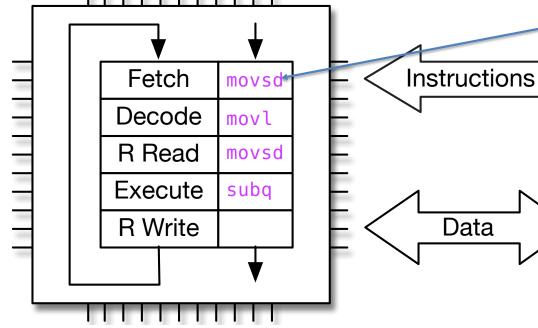

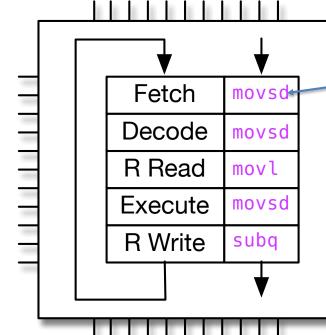

#### Execution Pipeline

- Stages of functionality to process issued instructions

- Hazards are conflicts with continued execution

- Forwarding supports closely associated operations exhibiting precedence constraints

#### Out of Order Execution

- Uses reservation stations

- Hides some core latencies and provide fine grain asynchronous operation supporting concurrency

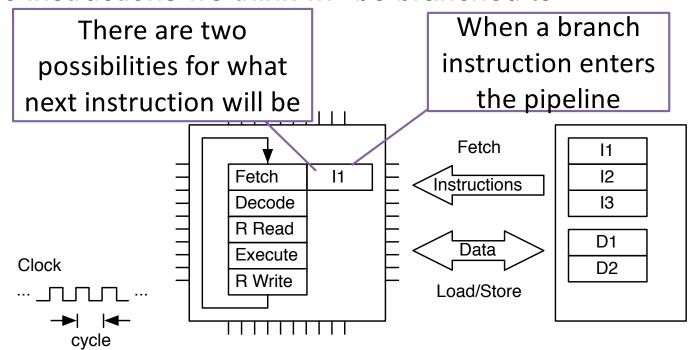

#### Branch Prediction

- Permits computation to proceed at a conditional branch point prior to resolving predicate value

- Overlaps follow-on computation with predicate resolution

- Requires roll-back or equivalent to correct false guesses

- Sometimes follows both paths, and several deep

# **Skylake**

NORTHWEST INSTITUTE for ADVANCED COMPUTING

AMATH 483/583 High-Performance Scien University of Washington by Ar Memory Subsystem

RY UNIVERSITY of WASHINGTON

#### **Microprocessors**

Basic operation: read and execute program instructions stored in memory

Fundamental performance / efficiency metric: cycles per instruction (CPI) also FL( Instructions can only be Fetch run in CPU Instructions **Transitions CPU** Memory Clock move data Data through CPU Program Load/Store cycle Data can only instructions be operated and data on in CPU NORTHWEST INSTITUTE for ADVANCED CUMPUTING

AMATH 483/583 High-Performance Scientific Computing Spring 2019 University of Washington by Andrew Lumsdaine

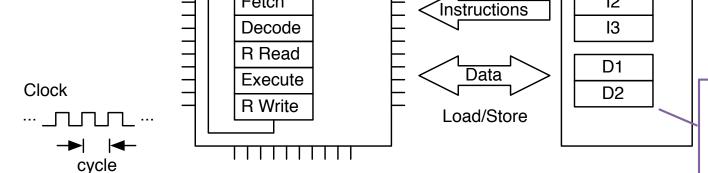

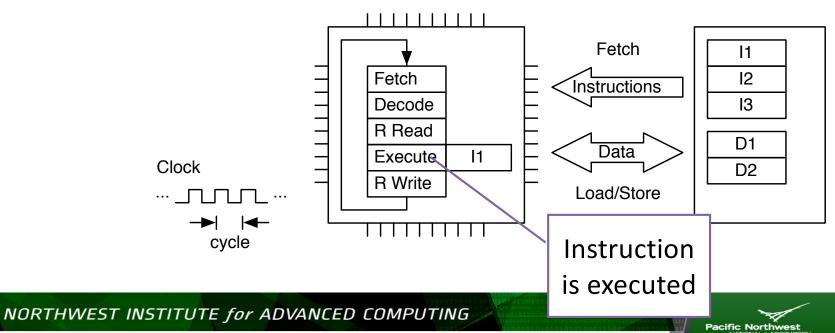

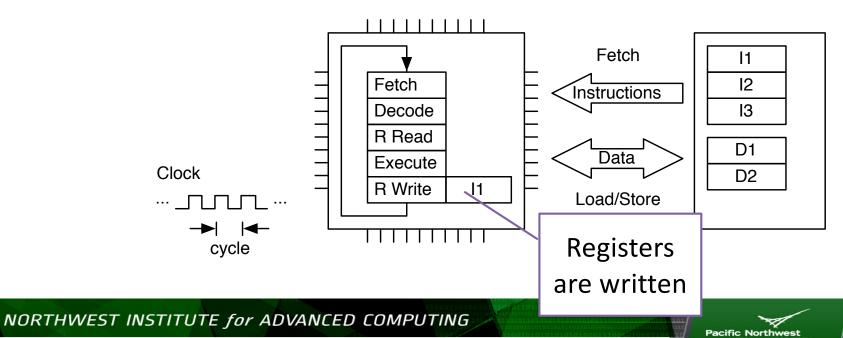

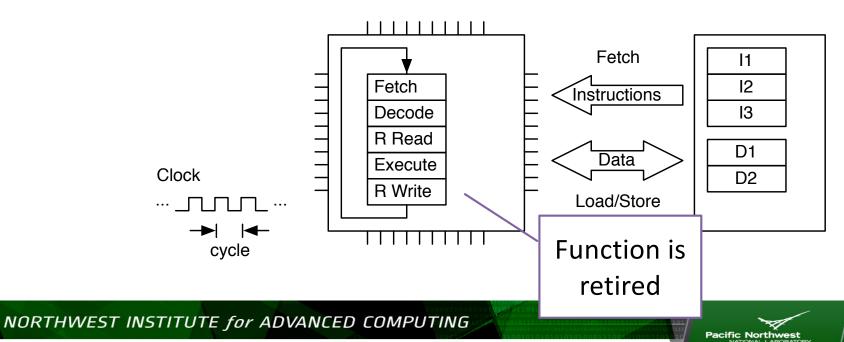

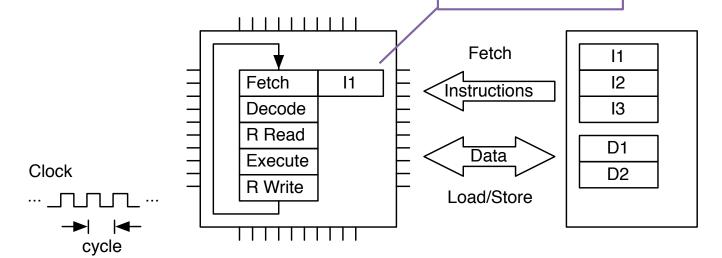

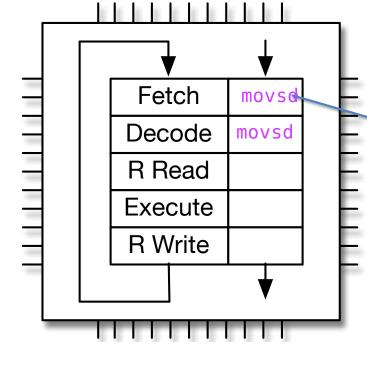

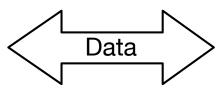

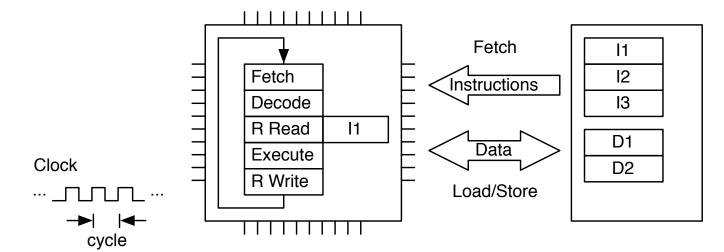

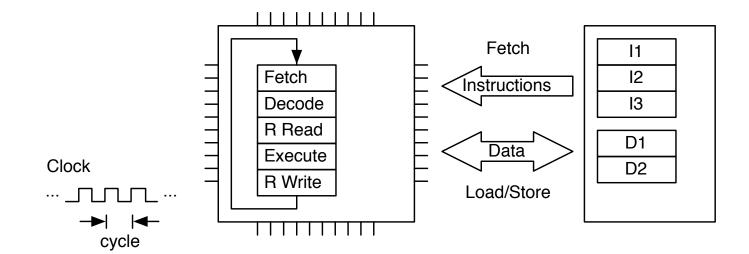

A single instruction may require multiple steps from fetch to

**Fetch**

completion

Instruction is returned

CPU Sends address to memory

Fetch

Fetch

Instruction instructions

Program Data

NORTHWEST INSTITUTE for ADVANCED COMPUTING

12

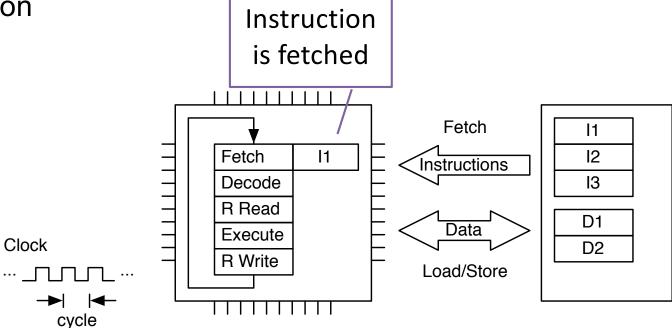

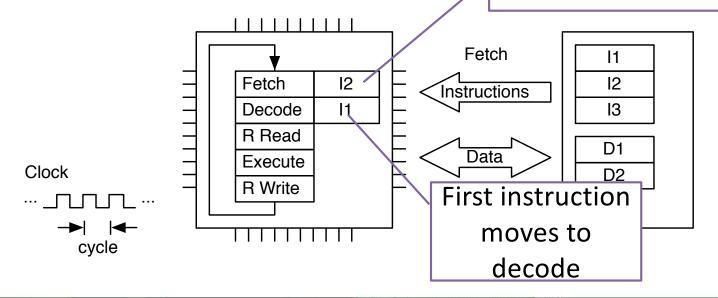

A single instruction may require multiple steps from fetch to

completion

A single instruction may require multiple steps from fetch to

completion Instruction is decoded Fetch 11 Fetch 12 Instructions 13 Decode 11 R Read D<sub>1</sub> Data Execute Clock D2 R Write Load/Store

NORTHWEST INSTITUTE for ADVANCED COMPUTING

cycle

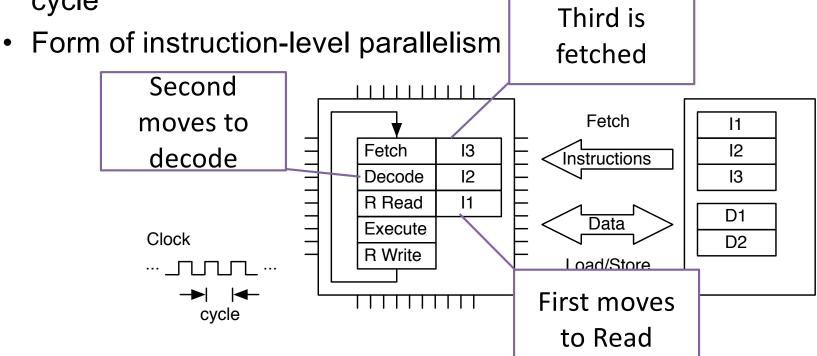

• A single instruction may require multiple steps from fetch to

completion

Registers

A single instruction may require multiple steps from fetch to completion

A single instruction may require multiple steps from fetch to completion

A single instruction may require multiple steps from fetch to completion

A single instruction may require multiple steps from fetch to

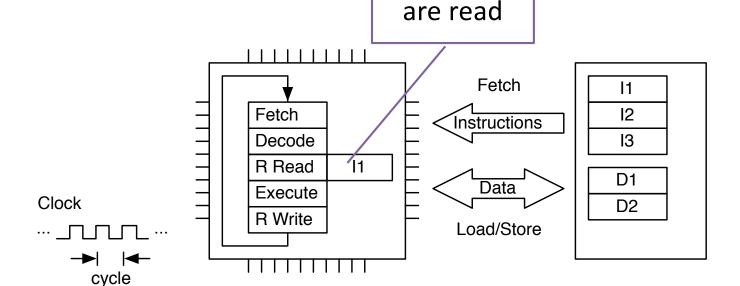

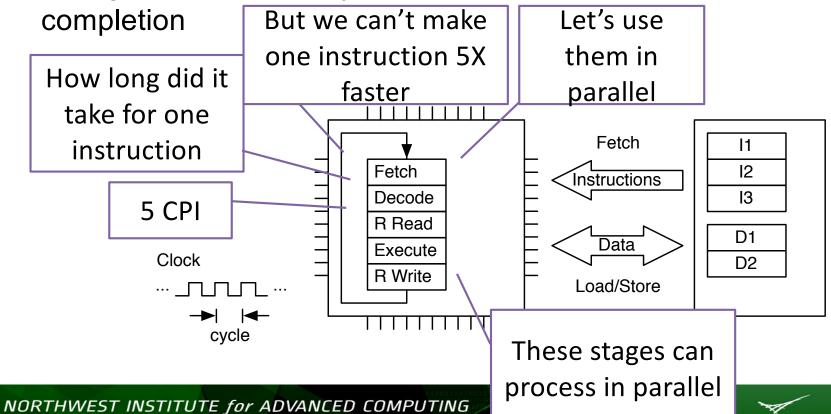

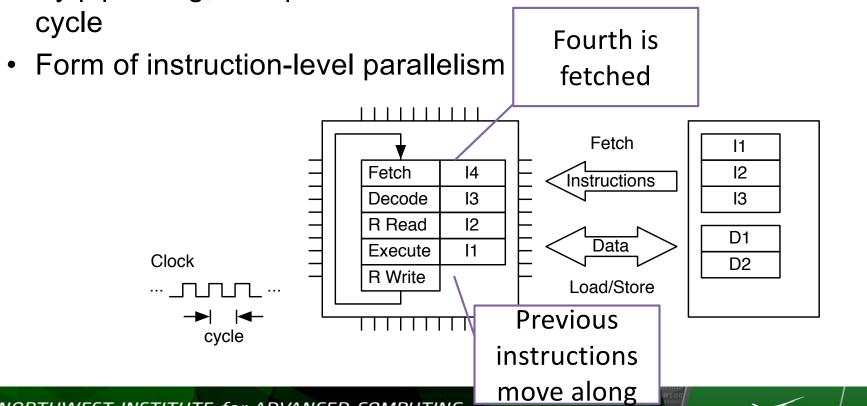

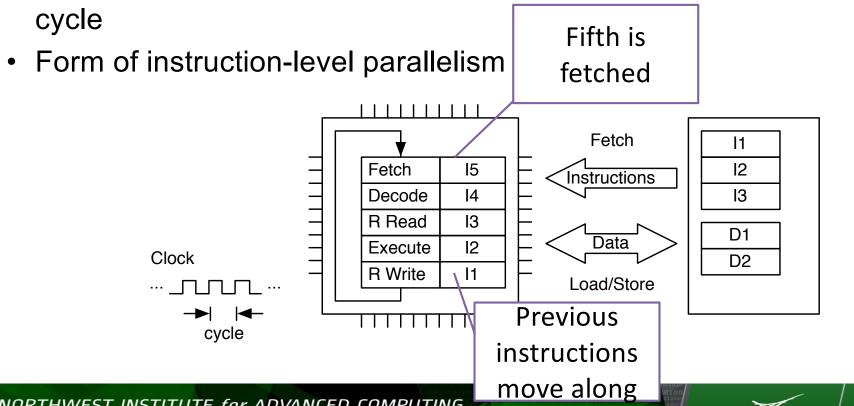

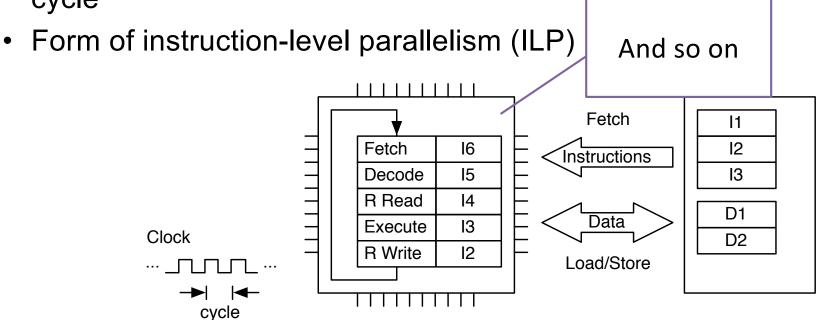

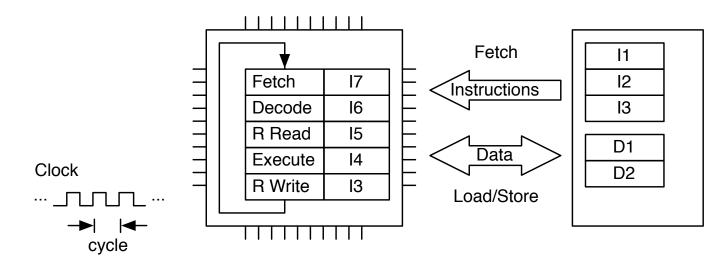

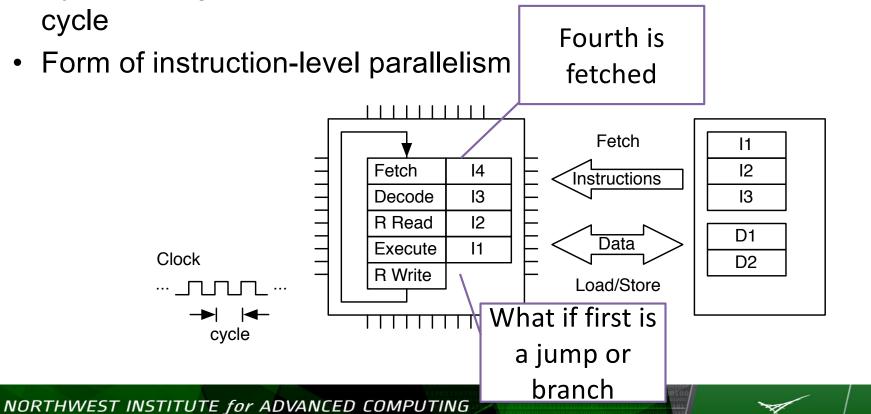

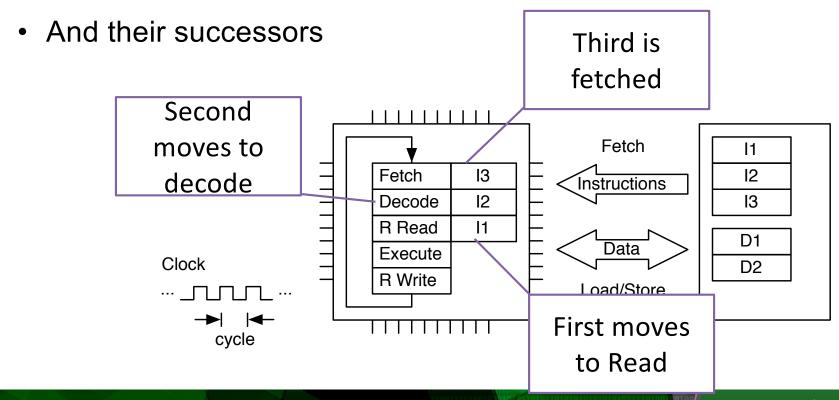

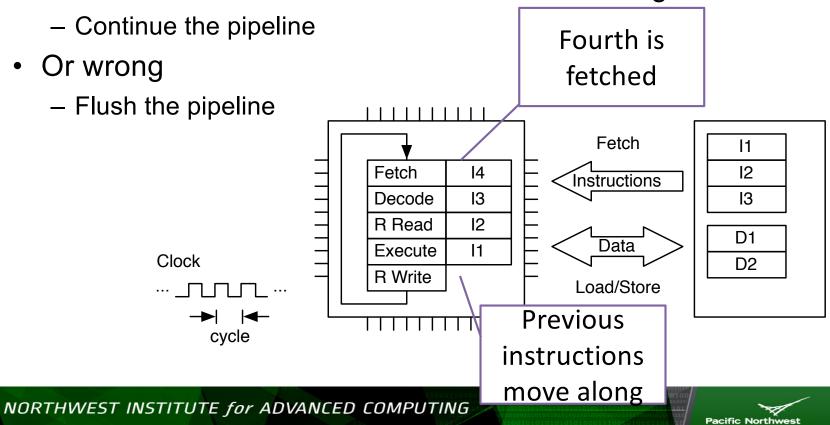

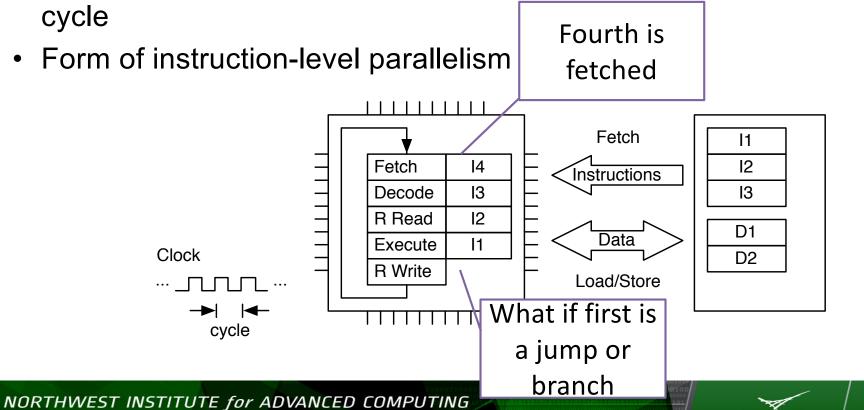

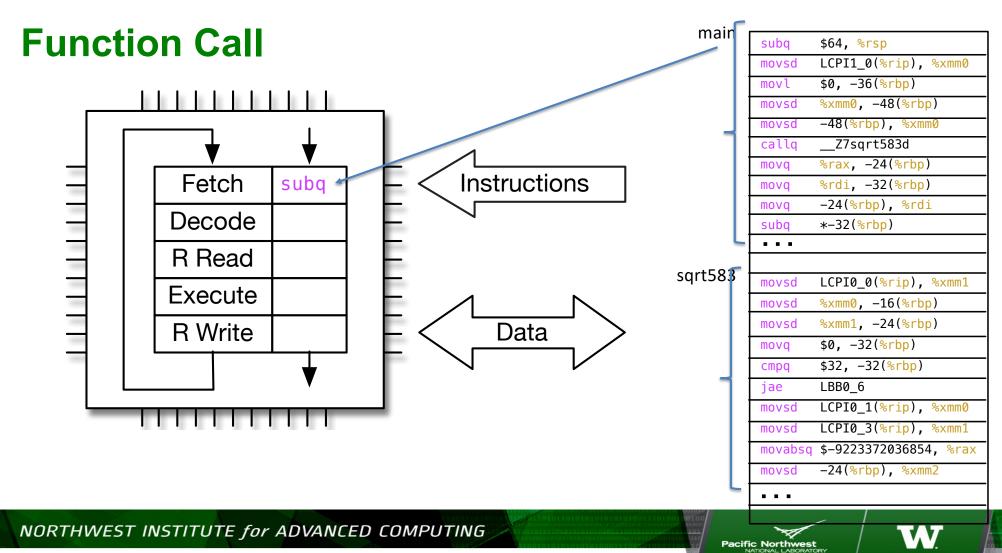

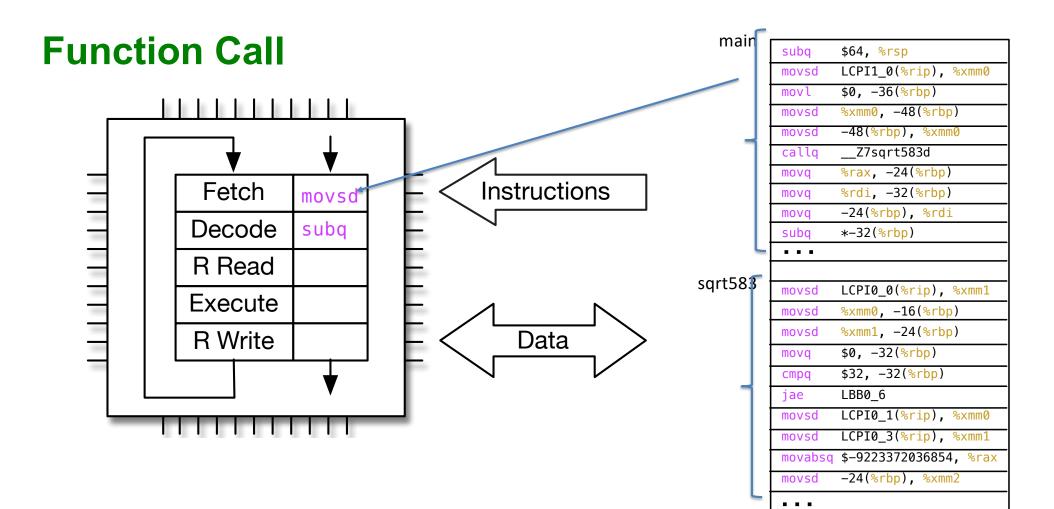

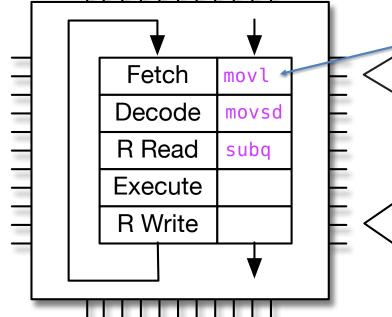

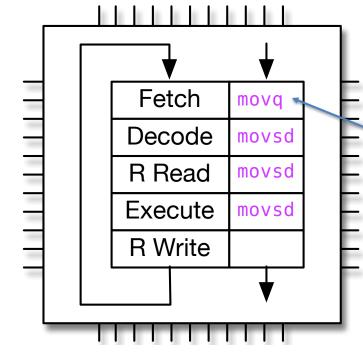

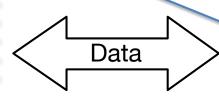

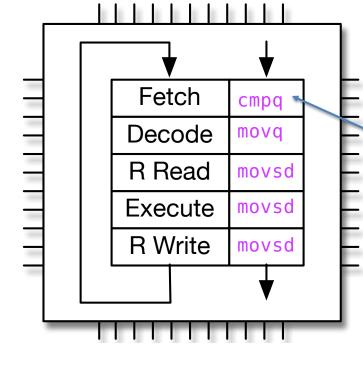

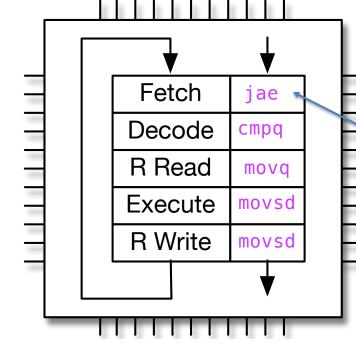

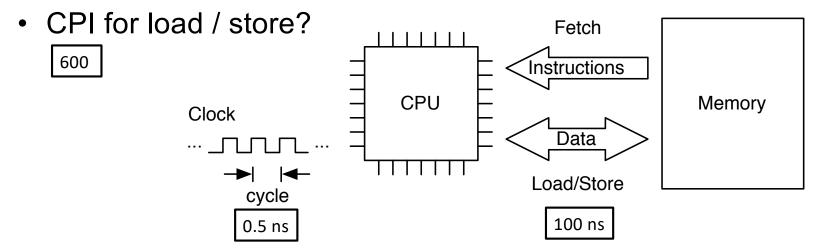

By pipelining, multiple instructions can be executed at each clock

cycle

Form of instruction-level parallelism (ILF)

Fetch first instruction

By pipelining, multiple instructions can be executed at each clock

cycle

Form of instruction-level parallelism (ILP)

When first instruction is in decode, fetch second

By pipelining, multiple instructions can be executed at each clock

cycle

By pipelining, multiple instructions can be executed at each clock

By pipelining, multiple instructions can be executed at each clock

By pipelining, multiple instructions can be executed at each clock

cycle

- By pipelining, multiple instructions can be executed at each clock cycle

- Form of instruction-level parallelism (ILP)

By pipelining, multiple instructions can be executed at each clock

By pipelining, multiple instructions can be executed at each clock

AMATH 483/583 High-Performance Scientific Computing Spring 2019 University of Washington by Andrew Lumsdaine

• A single instruction may require multiple steps from fetch to

completion

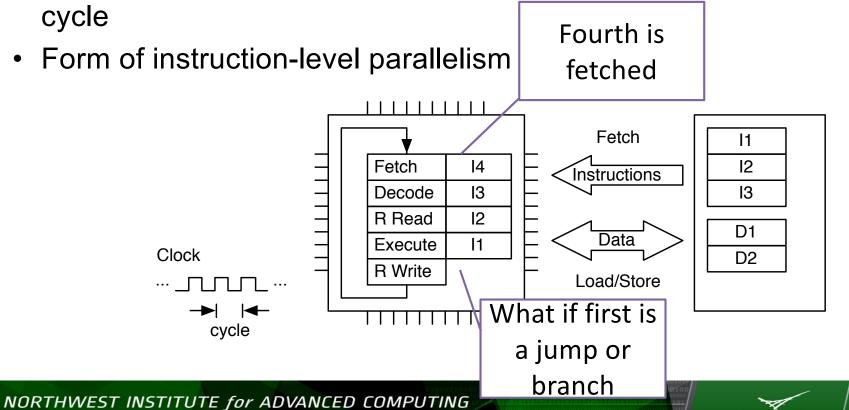

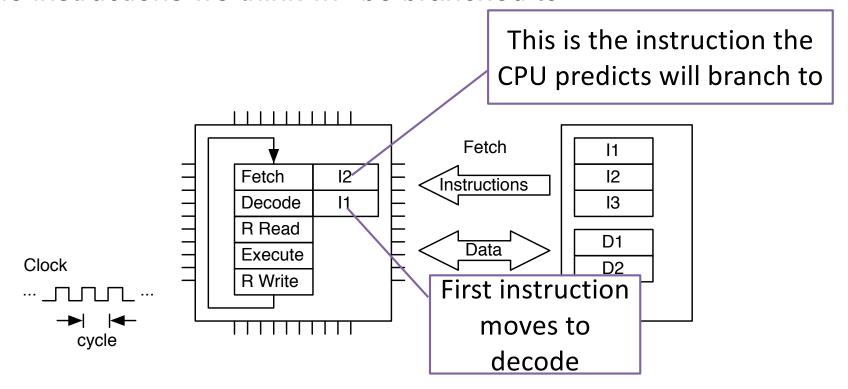

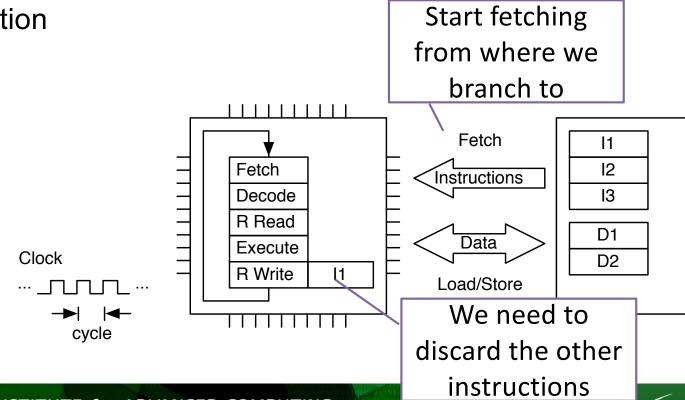

Start fetching from where we branch to

#### **Branch Prediction**

Load the instructions we think will be branched to

#### **Branch Prediction**

Load the instructions we think will be branched to

#### **Branch Prediction**

Load the instructions we think will be branched to

# **Instruction Pipelining**

28

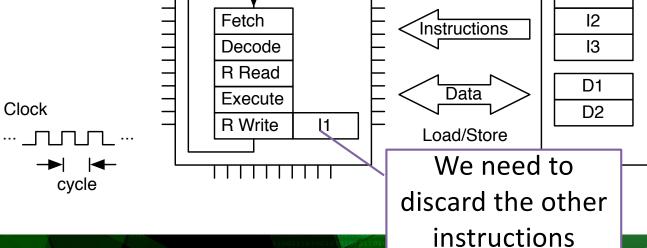

When instruction is executed we were either right

## **Pipeline Stall from Mis-Predict**

A single instruction may require multiple steps from fetch to completion

Start fetching

#### Performance-Oriented Architecture Features

#### **Execution Pipeline**

- Stages of functionality to process issued instructions

- Hazards are conflicts with continued execution

- Forwarding supports closely associated operations exhibiting precedence constraints

#### Out of Order Execution

- Uses reservation stations

- Hides some core latencies and provide fine grain asynchronous operation supporting concurrency

#### **Branch Prediction**

- Permits computation to proceed at a conditional branch point prior to resolving predicate value

- Overlaps follow-on computation with predicate resolution

- Requires roll-back or equivalent to correct false guesses

- Sometimes follows both paths, and several deep

By pipelining, multiple instructions can be executed at each clock

AMATH 483/583 High-Performance Scientific Computing Spring 2019

University of Washington by Andrew Lumsdaine

A single instruction may require multiple steps from fetch to

Start fetching completion from where we branch to Fetch 11 **Fetch** 12 Instructions 13 Decode R Read D<sub>1</sub> Data Execute Clock D2 R Write 11 Load/Store We need to cycle discard the other instructions

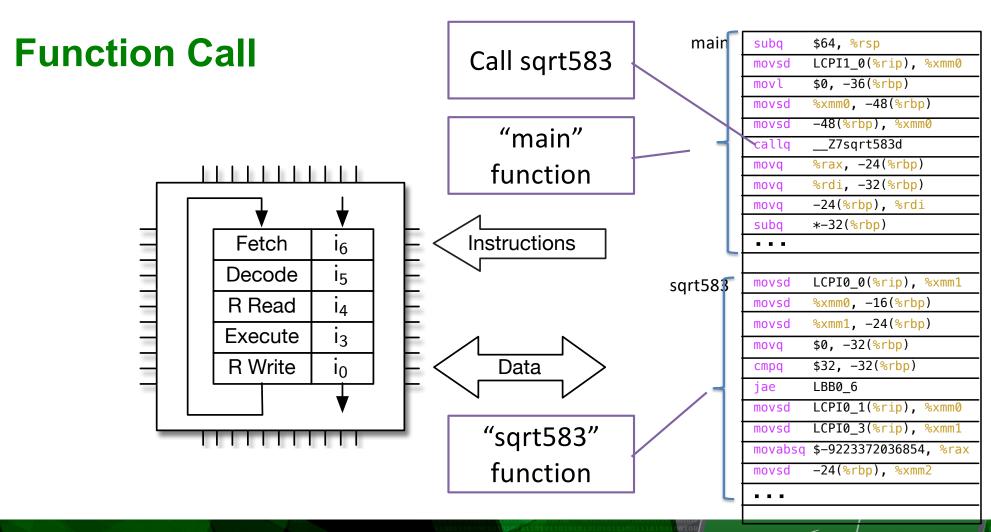

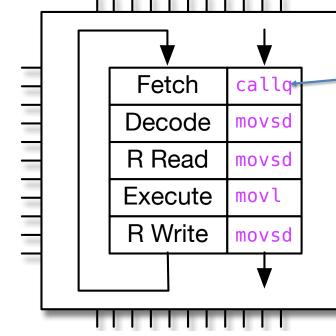

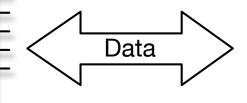

**Compiling functions**

```

#include <iostream>

#include <cmath>

double sqrt583(double z) {

double x = 1.0;

for (size_t i = 0; i < 32; ++i) {

double dx = -(x*x-z) / (2.0*x);

x += dx;

if (abs(dx) < 1.e-9) break;

return x;

int main () {

std::cout << sqrt583(2.0) << std::endl;

return 0;

```

\$ c++ main.cpp \$ ./a.out Compile main.cpp 1.4142 Translate it into a language the cpu can run \$ c++ main.cpp The executable (program that the cpu can run) \$ ./a.out

But what is this really?

**Compiled language**

```

#include <iostream>

#include <cmath>

double sqrt583(double z) {

double x = 1.0;

for (size_t i = 0; i < 32; ++i) {

double dx = -(x*x-z) / (2.0*x);

x += dx;

if (abs(dx) < 1.e-9) break;

return x;

int main () {

std::cout << sqrt583(2.0) << std::endl;

return 0;

```

\$ c++ main.cpp

sqrt583

main

| subq    | \$64, %rsp             |

|---------|------------------------|

| movsd   | LCPI1_0(%rip), %xmm0   |

| movl    | \$0, -36(%rbp)         |

| movsd   | %xmm0, -48(%rbp)       |

| movsd   | -48(%rbp), %xmm0       |

| callq   | Z7sqrt583d             |

| movq    | %rax, -24(%rbp)        |

| movq    | %rdi, -32(%rbp)        |

| movq    | -24(%rbp), %rdi        |

| subq    | *-32(%rbp)             |

|         |                        |

|         |                        |

| movsd   | LCPI0_0(%rip), %xmm1   |

| movsd   | %xmm0, -16(%rbp)       |

| movsd   | %xmm1, -24(%rbp)       |

| movq    | \$0, −32(%rbp)         |

| cmpq    | \$32, -32(%rbp)        |

| jae     | LBB0_6                 |

| movsd   | LCPI0_1(%rip), %xmm0   |

| movsd   | LCPI0_3(%rip), %xmm1   |

| movabsq | \$-9223372036854, %rax |

| movsd   | -24(%rbp), %xmm2       |

|         |                        |

|         |                        |

Pacific Northwest

NATIONAL LABORATORY

Proutly Operated by Battele

for the U.S. Department of Evergy

main

sqrt583

| 9 8 8 9 | 40:1 0:0p            |

|---------|----------------------|

| movsd   | LCPI1_0(%rip), %xmm0 |

| movl    | \$0, −36(%rbp)       |

| movsd   | %xmm0, -48(%rbp)     |

| movsd   | -48(%rbp), %xmm0     |

| callq   | Z7sqrt583d           |

| movq    | %rax, -24(%rbp)      |

| movq    | %rdi, -32(%rbp)      |

| movq    | -24(%rbp), %rdi      |

| subq    | *-32(%rbp)           |

|         |                      |

|         |                      |

\$64, %rsp

movsd LCPI0\_0(%rip), %xmm1

movsd %xmm0, -16(%rbp)

movsd %xmm1, -24(%rbp)

movq \$0, -32(%rbp)

cmpq \$32, -32(%rbp)

jae LBB0\_6

movsd LCPI0\_1(%rip), %xmm0

movsd LCPI0\_3(%rip), %xmm1

movabsq \$-9223372036854, %rax

movsd -24(%rbp), %xmm2

. . .

main

sqrt583

|   | subq  | \$64, %rsp           |

|---|-------|----------------------|

|   | movsd | LCPI1_0(%rip), %xmm0 |

|   | movl  | \$0, −36(%rbp)       |

|   | movsd | %xmm0, -48(%rbp)     |

| 1 | movsd | -48(%rbp), %xmm0     |

| 1 | callq | Z7sqrt583d           |

|   | movq  | %rax, -24(%rbp)      |

|   | movq  | %rdi, -32(%rbp)      |

|   | movq  | -24(%rbp), %rdi      |

|   | subq  | *-32(%rbp)           |

| ١ |       |                      |

|   |       |                      |

|   | movsd | LCPI0_0(%rip), %xmm1 |

|   | movsd | %xmm0, -16(%rbp)     |

|   | movsd | %xmm1, -24(%rbp)     |

|   |       |                      |

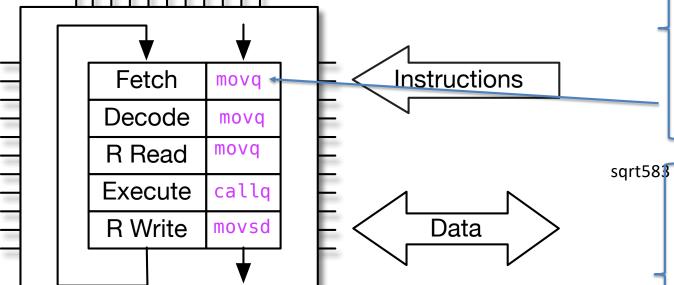

Data

\$0, -32(%rbp) movq \$32, -32(%rbp) cmpq LBB0\_6 jae LCPI0\_1(%rip), %xmm0 LCPI0\_3(%rip), %xmm1 movabsq \$-9223372036854, %rax -24(%rbp), %xmm2

. . .

main

| 5059  | ψο 1 / 01 ο β        |

|-------|----------------------|

| movsd | LCPI1_0(%rip), %xmm0 |

| movl  | \$0, −36(%rbp)       |

| movsd | %xmm0, -48(%rbp)     |

| movsd | -48(%rbp), %xmm0     |

| callq | Z7sqrt583d           |

| movq  | %rax, -24(%rbp)      |

| movq  | %rdi, -32(%rbp)      |

| movq  | -24(%rbp), %rdi      |

| subq  | *-32(%rbp)           |

|       |                      |

|       |                      |

LCPI0\_0(%rip), %xmm1

\$64. %rsp

sqrt583 movsd

movsd %xmm0, -16(%rbp)

movsd %xmm1, -24(%rbp)

movq \$0, -32(%rbp)

cmpq \$32, -32(%rbp)

jae LBB0\_6

movsd LCPI0\_1(%rip), %xmm0

movsd LCPI0\_3(%rip), %xmm1

movabsq \$-9223372036854, %rax movsd -24(%rbp), %xmm2

. . .

NORTHWEST INSTITUTE for ADVANCED COMPUTING

Pacific Northwest

NATIONAL LABORATORY

Peculity Operated by Batteste

for the U.S. Department of Evergy

main

sqrt583

| Subq  | \$04, 813p           |

|-------|----------------------|

| movsd | LCPI1_0(%rip), %xmm0 |

| movl  | \$0, −36(%rbp)       |

| movsd | %xmm0, -48(%rbp)     |

| movsd | -48(%rbp), %xmm0     |

| callq | Z7sqrt583d           |

| movq  | %rax, -24(%rbp)      |

| movq  | %rdi, -32(%rbp)      |

| movq  | -24(%rbp), %rdi      |

| subq  | *-32(%rbp)           |

|       |                      |

|       |                      |

\$64. %rsn

movsd LCPI0\_0(%rip), %xmm1

movsd %xmm0, -16(%rbp)

movsd %xmm1, -24(%rbp)

movq \$0, -32(%rbp)

cmpq \$32, -32(%rbp)

jae LBB0\_6

movsd LCPI0\_1(%rip), %xmm0

movsd LCPI0\_3(%rip), %xmm1

movabsq \$-9223372036854, %rax movsd -24(%rbp), %xmm2

. . .

NORTHWEST INSTITUTE for ADVANCED COMPUTING

Pacific Northwest

NATIONAL LABORATORY

Peauly Operated by Battelle

for the U.S. Department of Evergy

Pacific Northwest

main \$64, %rsp subg LCPI1\_0(%rip), %xmm0 movsd \$0, -36(%rbp) movl %xmm0, -48(%rbp) movsd -48(%rbp), %xmm0 movsd Z7sqrt583d callq %rax, -24(%rbp) movq %rdi, -32(%rbp) mova -24(%rbp), %rdi movq \*-32(%rbp) suba . . . LCPI0\_0(%rip), %xmm1 movsd %xmm0, -16(%rbp) movsd %xmm1, -24(%rbp) movsd \$0, -32(%rbp) movq \$32, -32(%rbp) cmpq LBB0 6 jae LCPIO\_1(%rip), %xmm0 LCPI0\_3(%rip), %xmm1 movabsq \$-9223372036854, %rax -24(%rbp), %xmm2 movsd . . .

NORTHWEST INSTITUTE for ADVANCED COMPUTING

Pacific Northwest

NATIONAL LABORATORY

Peculty Operated by Battelle

for the U.S. Department of Evergy

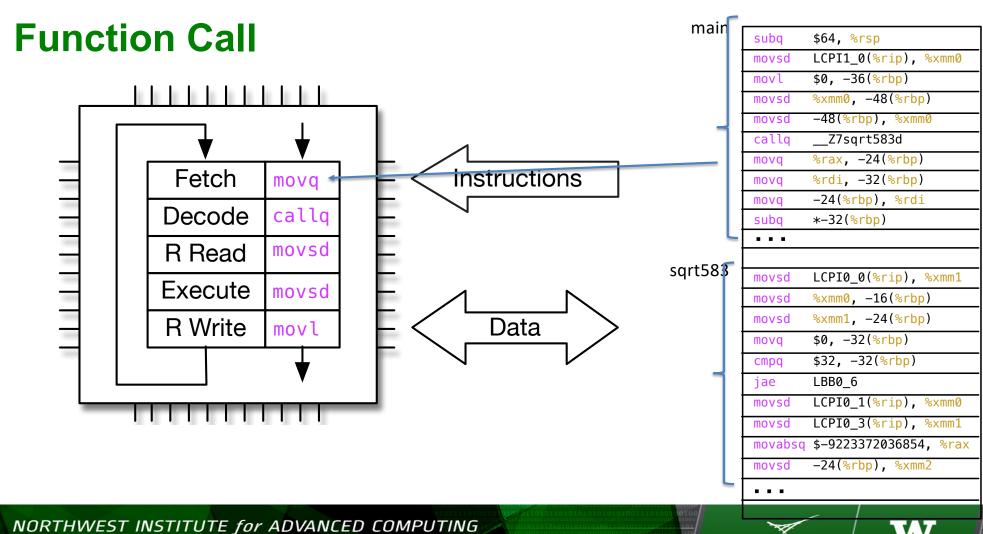

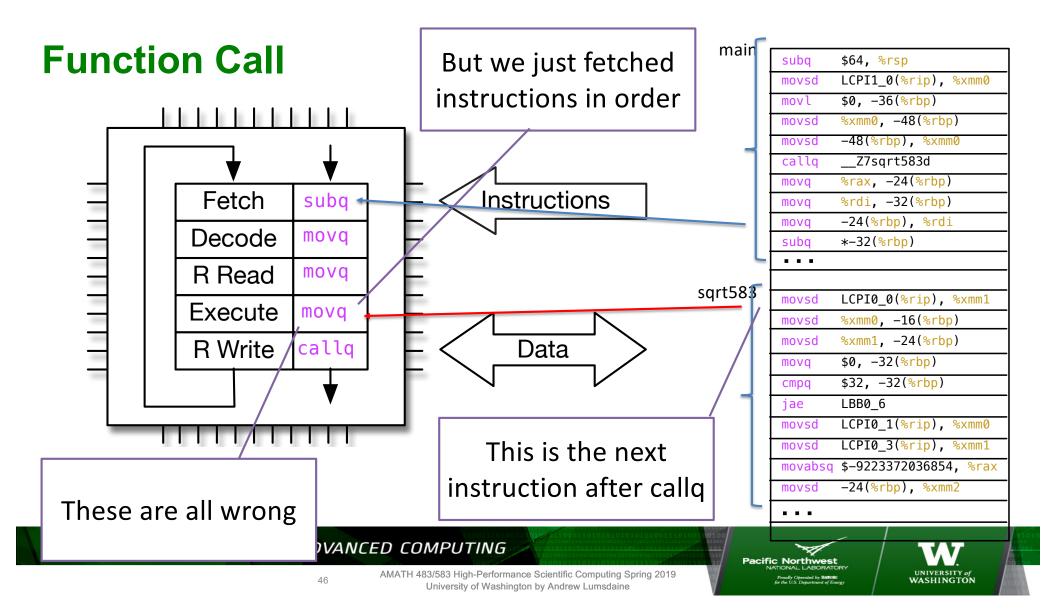

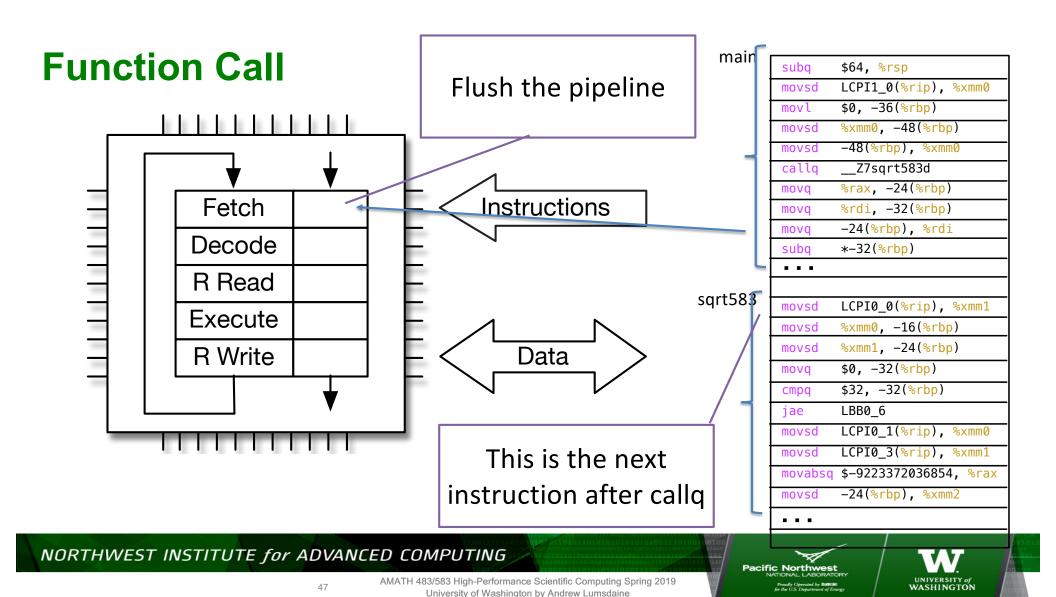

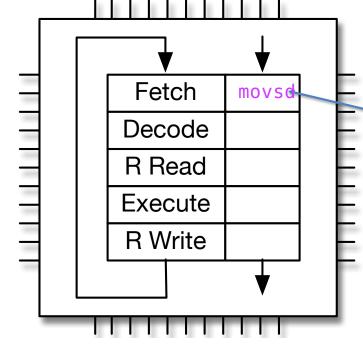

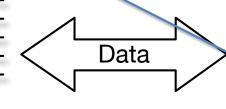

Instructions

This is the next instruction after callq

main

sqrt583

|   |       | - 1                  |

|---|-------|----------------------|

|   | movsd | LCPI1_0(%rip), %xmm0 |

|   | movl  | \$0, −36(%rbp)       |

|   | movsd | %xmm0, -48(%rbp)     |

|   | movsd | -48(%rbp), %xmm0     |

|   | callq | Z7sqrt583d           |

|   | movq  | %rax, -24(%rbp)      |

|   | movq  | %rdi, -32(%rbp)      |

|   | movq  | -24(%rbp), %rdi      |

|   | subq  | *-32(%rbp)           |

| ١ |       |                      |

|   |       |                      |

\$64, %rsp

LCPI0\_0(%rip), %xmm1 movsd movsd %xmm0, -16(%rbp) %xmm1, -24(%rbp) movsd \$0, -32(%rbp) movq \$32, -32(%rbp) cmpq LBB0\_6 jae LCPI0\_1(%rip), %xmm0 LCPI0\_3(%rip), %xmm1 movabsq \$-9223372036854, %rax -24(%rbp), %xmm2

| - - -

Instructions

This is the next instruction after callq

main

sqrt583

| 3459  | φσι, σιορ            |

|-------|----------------------|

| movsd | LCPI1_0(%rip), %xmm0 |

| movl  | \$0, −36(%rbp)       |

| movsd | %xmm0, -48(%rbp)     |

| movsd | -48(%rbp), %xmm0     |

| callq | Z7sqrt583d           |

| movq  | %rax, -24(%rbp)      |

| movq  | %rdi, -32(%rbp)      |

| movq  | -24(%rbp), %rdi      |

| subq  | *-32(%rbp)           |

|       |                      |

|       |                      |

\$64. %rsp

| movsd   | LCPI0_0(%rip), %xmm1   |

|---------|------------------------|

| movsd   | %xmm0, -16(%rbp)       |

| movsd   | %xmm1, -24(%rbp)       |

| movq    | \$0, -32(%rbp)         |

| cmpq    | \$32, -32(%rbp)        |

| jae     | LBB0_6                 |

| movsd   | LCPIO_1(%rip), %xmm0   |

| movsd   | LCPIO_3(%rip), %xmm1   |

| movabsq | \$-9223372036854, %rax |

| movsd   | -24(%rbp), %xmm2       |

|         |                        |

NORTHWEST INSTITUTE for ADVANCED COMPUTING

Pacific Northwest

NATIONAL LABORATOR'

Proudly Operated by Battele

for the U.S. Department of Energy

Instructions

This is the next instruction after callq

main

sqrt583

| Subq  | 304, 613p            |

|-------|----------------------|

| movsd | LCPI1_0(%rip), %xmm0 |

| movl  | \$0, −36(%rbp)       |

| movsd | %xmm0, -48(%rbp)     |

| movsd | -48(%rbp), %xmm0     |

| callq | Z7sqrt583d           |

| movq  | %rax, -24(%rbp)      |

| movq  | %rdi, -32(%rbp)      |

| movq  | -24(%rbp), %rdi      |

| subq  | *-32(%rbp)           |

|       |                      |

|       |                      |

| moved | ICDTA A(%rin) %vmm1  |

\$64. %rsn

| movsd   | <pre>LCPI0_0(%rip), %xmm1</pre> |

|---------|---------------------------------|

| movsd   | %xmm0, -16(%rbp)                |

| movsd   | %xmm1, -24(%rbp)                |

| movq    | \$0, -32(%rbp)                  |

| cmpq    | \$32, -32(%rbp)                 |

| jae     | LBB0_6                          |

| movsd   | LCPIO_1(%rip), %xmm0            |

| movsd   | LCPI0_3(%rip), %xmm1            |

| movabsq | \$-9223372036854, %rax          |

| movsd   | -24(%rbp), %xmm2                |

. . .

Instructions

This is the next instruction after callq

main

sqrt583

| Subq  | 304, %13p            |

|-------|----------------------|

| movsd | LCPI1_0(%rip), %xmm0 |

| movl  | \$0, −36(%rbp)       |

| movsd | %xmm0, -48(%rbp)     |

| movsd | -48(%rbp), %xmm0     |

| callq | Z7sqrt583d           |

| movq  | %rax, -24(%rbp)      |

| movq  | %rdi, -32(%rbp)      |

| movq  | -24(%rbp), %rdi      |

| subq  | *-32(%rbp)           |

|       |                      |

|       |                      |

| movsd   | <pre>LCPI0_0(%rip), %xmm1</pre> |

|---------|---------------------------------|

| movsd   | %xmm0, -16(%rbp)                |

| movsd   | %xmm1, -24(%rbp)                |

| movq    | \$0, -32(%rbp)                  |

| cmpq    | \$32, -32(%rbp)                 |

| jae     | LBB0_6                          |

| movsd   | LCPIO_1(%rip), %xmm0            |

| movsd   | LCPI0_3(%rip), %xmm1            |

| movabsq | \$-9223372036854, %rax          |

| movsd   | -24(%rbp), %xmm2                |

|         | <u> </u>                        |

Instructions

This is the next instruction after callq

main

sgrt583

| Subq  | 304, 813p            |

|-------|----------------------|

| movsd | LCPI1_0(%rip), %xmm0 |

| movl  | \$0, −36(%rbp)       |

| movsd | %xmm0, -48(%rbp)     |

| movsd | -48(%rbp), %xmm0     |

| callq | Z7sqrt583d           |

| movq  | %rax, -24(%rbp)      |

| movq  | %rdi, -32(%rbp)      |

| movq  | -24(%rbp), %rdi      |

| subq  | *-32(%rbp)           |

|       |                      |

|       |                      |

\$64. %rsn

LCPI0\_0(%rip), %xmm1 movsd movsd %xmm0, -16(%rbp) %xmm1, -24(%rbp) movsd \$0, -32(%rbp) movq \$32, -32(%rbp) cmpq LBB0\_6 jae LCPI0\_1(%rip), %xmm0 LCPI0\_3(%rip), %xmm1 movabsq \$-9223372036854, %rax -24(%rbp), %xmm2

. . .

Instructions

This is the next instruction after callq

main

sgrt583

|       | 1 - 1                |

|-------|----------------------|

| movsd | LCPI1_0(%rip), %xmm0 |

| movl  | \$0, −36(%rbp)       |

| movsd | %xmm0, -48(%rbp)     |

| movsd | -48(%rbp), %xmm0     |

| callq | Z7sqrt583d           |

| movq  | %rax, -24(%rbp)      |

| movq  | %rdi, -32(%rbp)      |

| movq  | -24(%rbp), %rdi      |

| subq  | *-32(%rbp)           |

|       |                      |

|       |                      |

\$64, %rsp

LCPI0\_0(%rip), %xmm1 movsd movsd %xmm0, -16(%rbp) %xmm1, -24(%rbp) movsd \$0, -32(%rbp) movq \$32, -32(%rbp) cmpq LBB0\_6 jae LCPI0\_1(%rip), %xmm0 LCPI0\_3(%rip), %xmm1 movabsq \$-9223372036854, %rax -24(%rbp), %xmm2

. . .

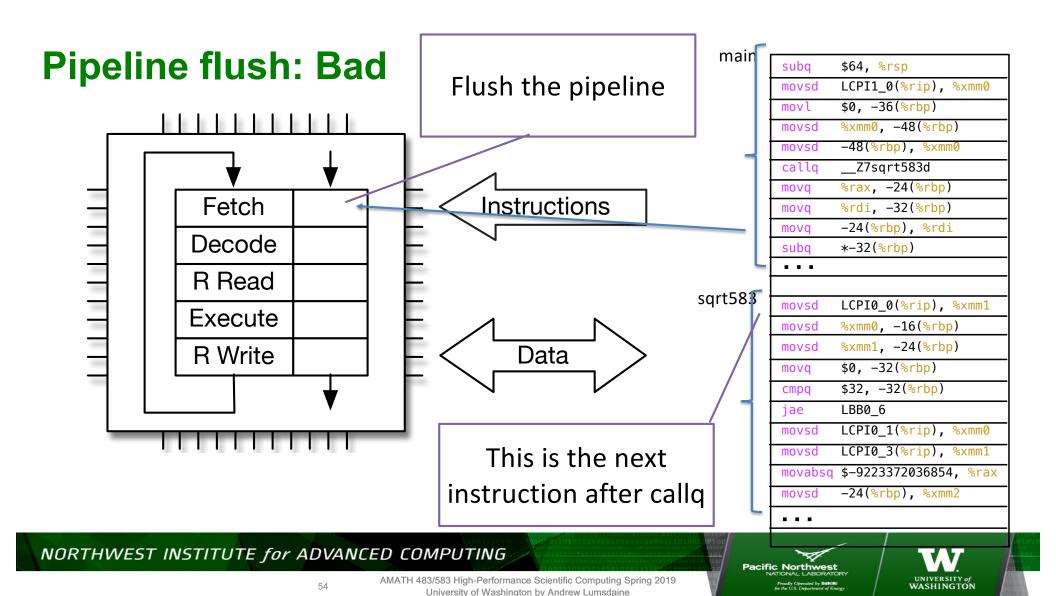

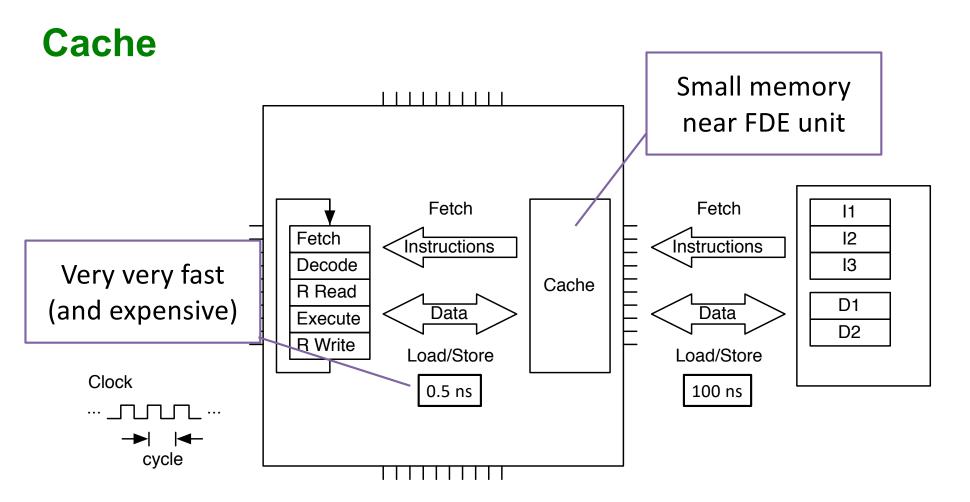

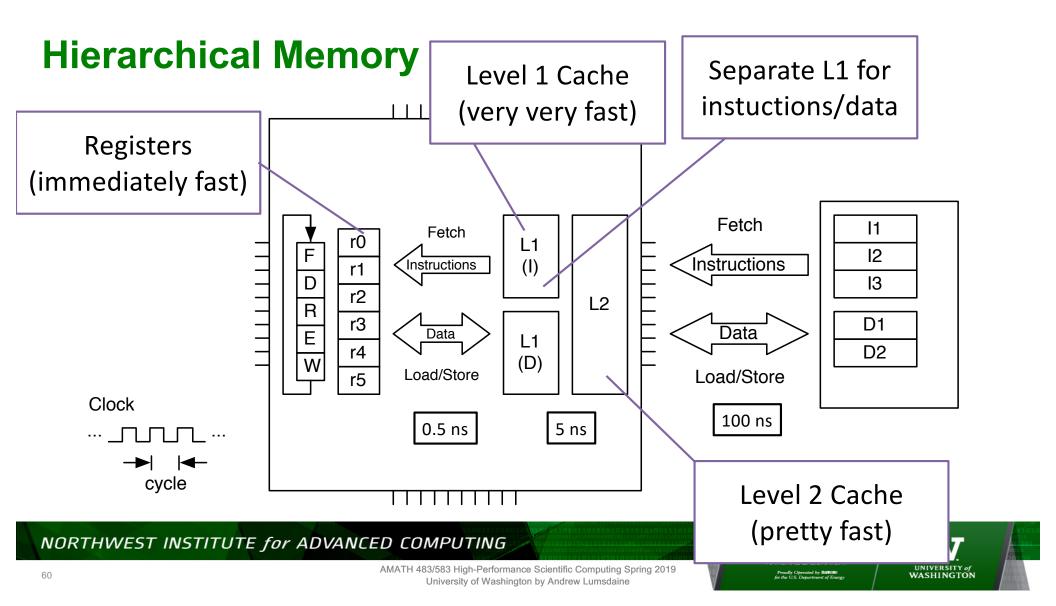

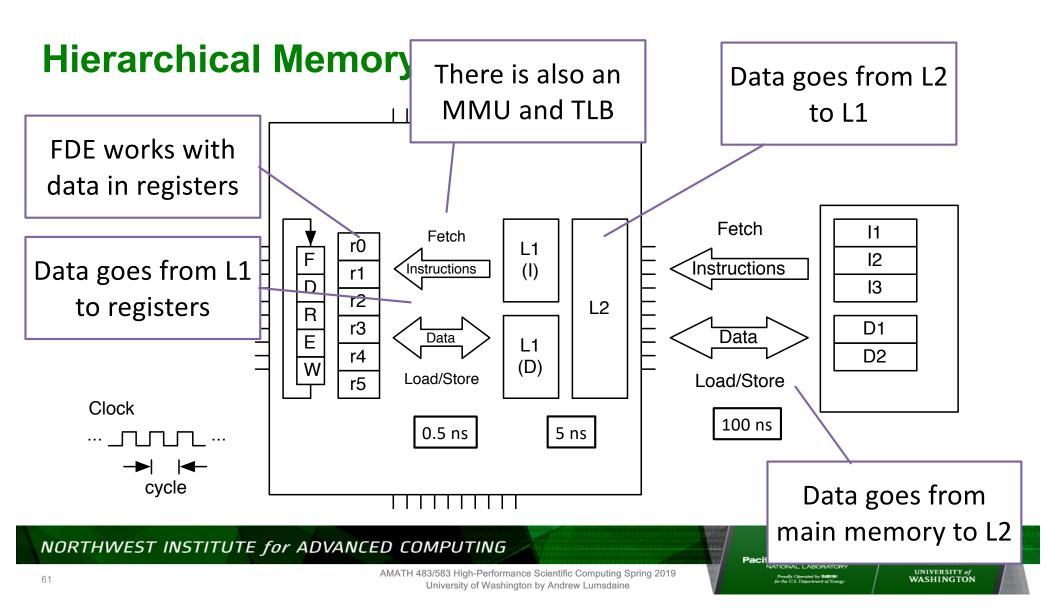

# **Memory Access**

- What are typical costs for accessing memory?

- What is typical clock cycle time?

- How many clock cycles to fetch an instruction?

- How many clock cycles to execute load / store instruction?

The next one may be cheaper

## **Memory Access Costs**

Access to main memory has huge impact on performance

## **Memory Access Costs**

- Access to main memory has huge impact on performance

- Latency: How long does the first access to data take

- Bandwidth: How much data can we continuously fetch

## **Memory Access Costs**

- Access to main memory has huge impact on performance (600X)

- Processor would be idle almost all the time

## **Performance**

NORTHWEST INSTITUTE for ADVANCED COMPUTING

AMATH 483/583 High-Performance Scientific Computing Spring 2019

University of Washington by Andrew Lumsdaine

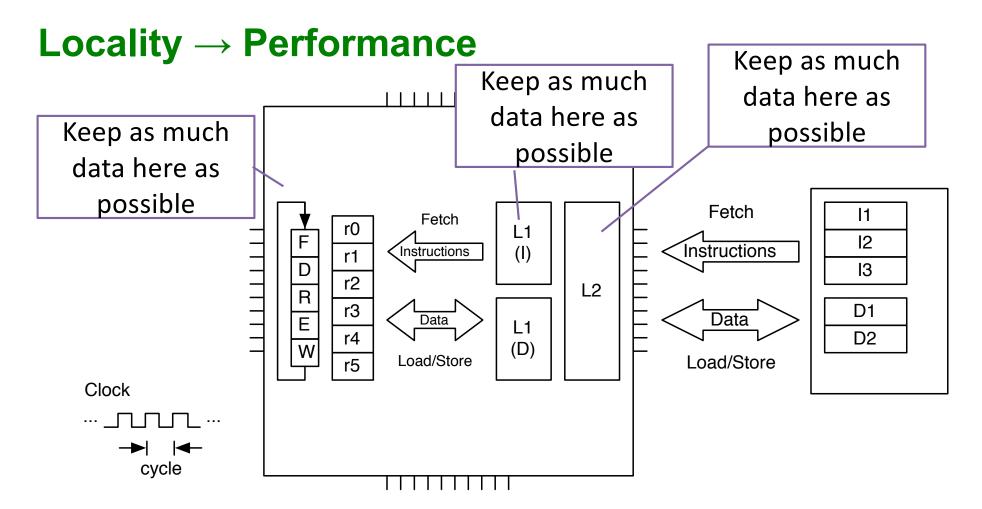

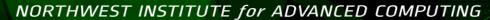

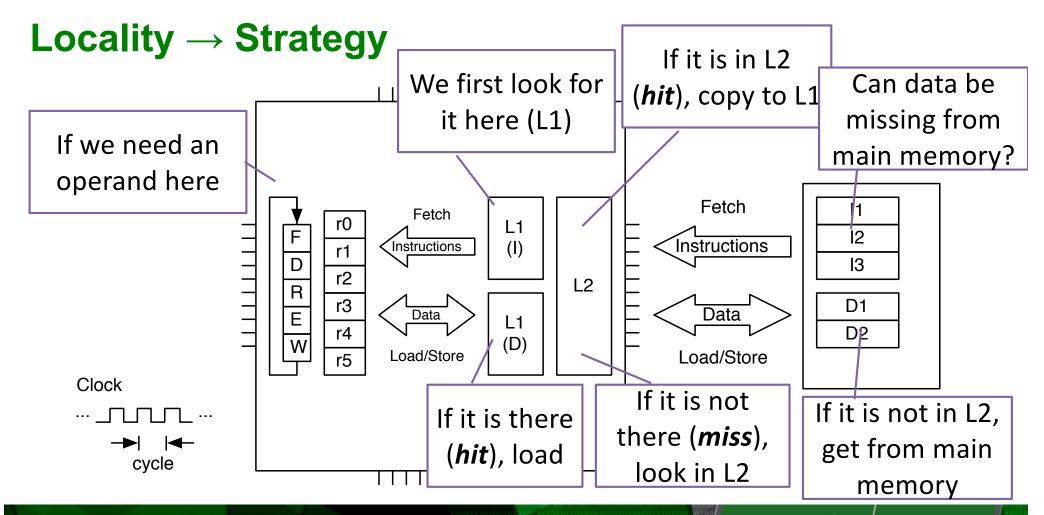

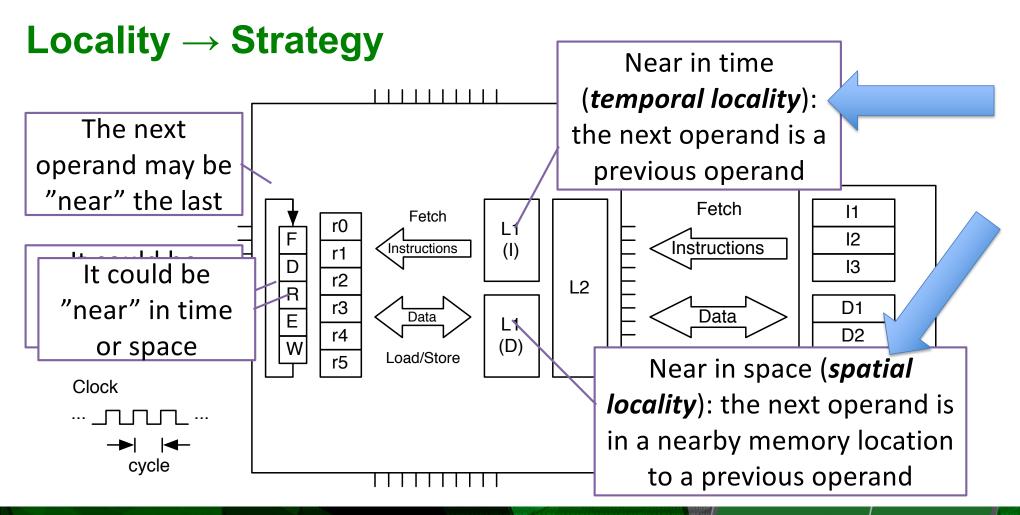

## **Locality** → **Performance**

- Caches are much smaller than main memory. How do we decide what data to keep in cache to effect higher performance (more accesses)?

- Temporal Locality: if a program accesses a memory location, there

is a much higher than random probability that the same location will

be accessed again

- Cache replacement policies attempt to keep cached elements in the cache for as long as possible

- Spatial Locality: if a program accesses a memory location, there is a much higher than random probability that nearby locations will also be accessed (soon)

- Cache policies read contiguous chunks of data a referenced element and its neighbors – not just single elements

#### **Matrix Vector Product**

• Recall for ANN  $x^{i+1} = S(W^i x^i)$

$x^{i+1} \leftarrow W^i \times x^i$  num\_cols()

• In general  $y \leftarrow A \times x$

$y_i = \sum_{i=0}^{N-1} A_{ij} x_j, \quad i = 0, \dots, M$

summation

Two nested loops

num\_rows()

```

for (size_t i = 0; i < A.num_rows(); ++i) {

for (size_t j = 0; j < A.num_cols(); ++j) {

y(i) += A(i, j) * x(j);

}

}

How many times

is this done?</pre>

```

How many flops?

How much data?

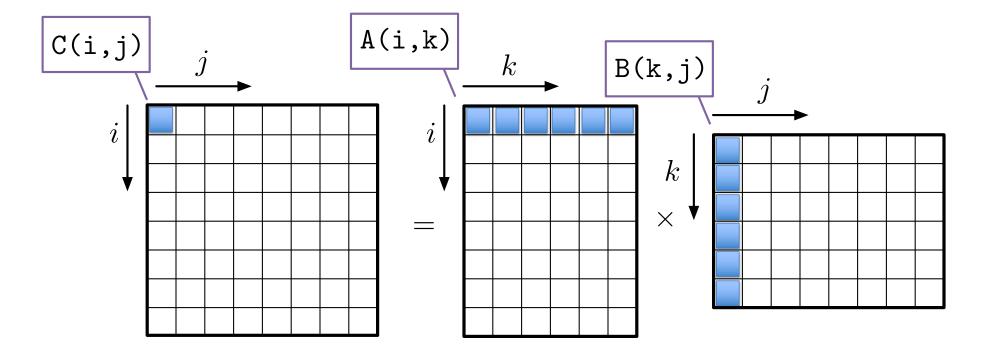

## **Matrix-matrix product**

```

C_{ij} = \sum_{k=0}^{K-1} A_{ik} B_{kj}

```

Three nested loops

```

for (size_t i = 0; i < C.num_rows(); ++i) {

for (size_t j = 0; j < C.num_cols(); ++j) {

for (size_t k = 0; k < A.num_cols(); ++k) {

C(i, j) += A(i, k) * B(k, j);

}

}

How many times

is this done?</pre>

```

How many flops?

How much

data?

## **Timing and Benchmarking**

- Humans have pathological need to see who is better at everything

- But ordering requires a single number corresponding to "goodness"

- Which is impossible of course

- So we take one task and turn that into the definition of goodness (cf IQ)

- (What is IQ? It's the thing that the IQ test measures.) My personal rant

- In HPC, we take performance on a particular computational task to rank the worlds computers with the 500 best scores on this task

- Linear system solution matrix matrix product at the core

- Performance = FLOPS = (Total computations) / (Time to compute)

- Linpack  $\rightarrow 2N^3$  / (Time to compute)

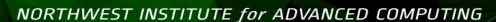

## **Timing a Program**

The time program in Linux (Unix) will measure time resources a process uses

Elapsed Wall Clock time

Time Spent running user code

Time Spent running system code

This is what we'll be using

But finer grained control

#### C++ Timer

# And this will be provided to you

```

class Timer {

private:

typedef std::chrono::time_point<std::chrono::system_clock> time_t;

All you need to

public:

Timer() : startTime(), stopTime() {}

worry about

time_t start()

{ return (startTime = std::chrono::system_clock::now()); }

time_t stop()

{ return (stopTime = std::chrono::system_clock::now()); }

double elapsed() { return

std::chrono::duration_cast<std::chrono::milliseconds>(stopTime-startTime).count(); }

private:

time_t startTime, stopTime;

};

```

#### **Measuring Matrix Matrix Product**

```

#include <iostream>

#include "Matrix.hpp"

#include "Timer.hpp"

using namespace std;

Declare Timer T

int main() {

cout << "N\tElapsed" << endl;</pre>

Start Timer T

for (int N = \%; N < 1024; N *= 2)

Matrix A(N, N), B(N, N), C(N, N), D(N, N);

Timer T; T.start();

A = B*C;

Stop Timer T

T.stop();___

cout << N << "\t" << T.elapsed() << endl;</pre>

And???

Print Elapsed Time

return 0:

```

Insufficient resolution

\$ ./a.out

N Elapsed

8 0

16 0

32 0

28

315

64

128

256

512

#### What All Are We Timing

Allocating a Matrix

Never allocate new memory in performance critical sections of code

#### **Just For Benchmarking**

```

Matrix operator*(const Matrix& A, const Matrix&B) {

Matrix C(A.num_rows(), B.num_cols());

zeroizeMatrix(C);

multiply(A, B, C);

return C;

C++ Core Guideline

Violation

void multiply(const Matrix& A, const Matrix&B, Matrix&C) {

for (size_t i = 0; i < A.num_rows(); ++i) {</pre>

F.20: For "out" output

for (size_t j = 0; j < B.num_cols(); ++j) {</pre>

for (size_t k = 0; k < A.num_cols(); ++k) {</pre>

values, prefer return

C(i,j) += A(i,k) * B(k,j);

values to output

parameters

```

#### **Benchmarking**

#### **Bonus Question (Advanced Topic)**

```

If we have different

double benchmark(int M, int N, int K, long n

multiply routines (and

Matrix A(M, K), B(K, N), C(M, N);

we will), how many of

Timer T;

these do we write?

T.start():

for (int i = 0; i < numruns; ++i) {</pre>

multiply(A, B, C);

By how much

T.stop();

do they differ?

How can we

return T.elapsed();

parameterize that?

}

```

#### **Bonus Question (Advanced Topic)**

```

We want to

double benchmark(int M, int N, int K, long n

<something> f) { ——

pass in

Matrix A(M, K), B(K, N), C(M, N);

something

Timer T;

Double bonus: It

T.start();

just needs an

for (int i = 0; i < numruns; ++i) {

f(A, B, C);

operator()()

That we call

like a function

T.stop();

Let's not get

return T.elapsed();

carried away

```

#### **Functions as Data**

```

Matrix& and a

Is a function

#include <functional>

Matrix& for args

double benchmark(int M, int N, int K, long numruns,

function < void (const Matrix&, const Matrix&, Matrix&)>f) {

Parameter f

Matrix A(M, K), B(K, N), C(M, N);

That returns

void

Timer T;

Like multiply()

T.start();

for (int i = 0; i < numruns; ++i) {

f(A, B, C);

void multiply(const Matrix& A, const Matrix&B, Matrix&C);

T.stop();

return T.elapsed();

```

And takes two const

#### **Functions as Data (Advanced)**

# Functions returning void

And taking two const Matrix& and a Matrix& for args

```

void multiply(const Matrix& A, const Matrix &B, Matrix& C);

void multiply_2(const Matrix& A, const Matrix &B, Matrix& C);

void yet_another(const Matrix& A, const Matrix &B, Matrix& C);

```

```

double t1 = benchmark(100, 100, 100, multiply);

double t2 = benchmark(100, 100, 100, multiply_2);

double t2 = benchmark(100, 100, 100, yet_another);

```

Pass them into another function

#### Let's Start Benchmarking

```

double benchmark(int M, int N, int K, long numruns) {

Matrix A(M, K), B(K, N), C(M, N);

Timer T;

T.start();

for (int i = 0; i < numruns; ++i) {

multiply(A, B, C);

}

T.stop();

bench: bench:

return T.elapsed();

}</pre>

```

```

bench: bench.o Matrix.o

c++ -std=c++11 bench.o Matrix.o -o bench

bench.o: bench.cpp Matrix.hpp

c++ -std=c++11 -c bench.cpp -o bench.o

Matrix.o: Matrix.cpp Matrix.hpp

c++ -std=c++11 -c Matrix.cpp -o Matrix.o

```

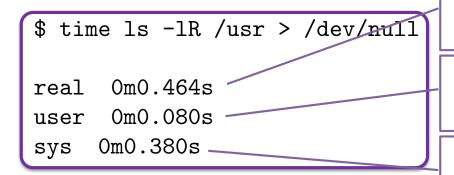

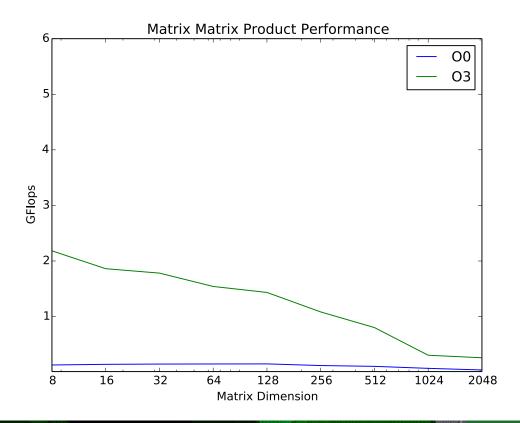

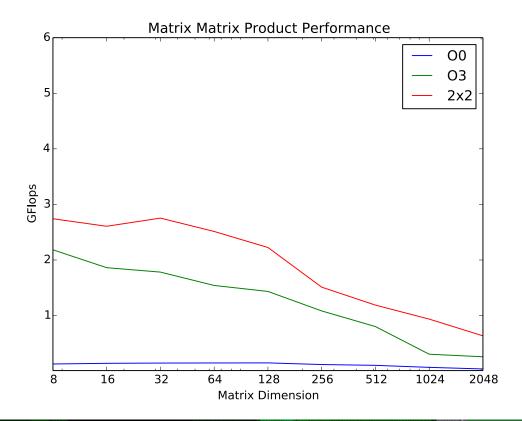

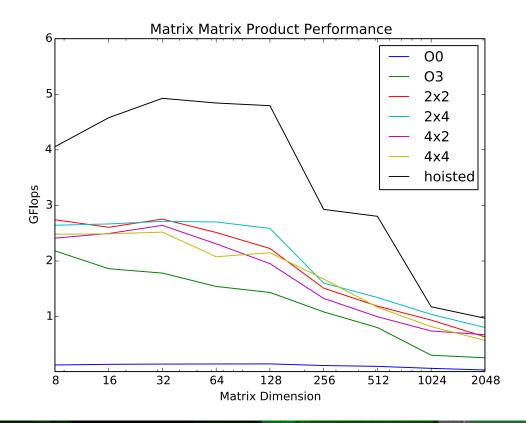

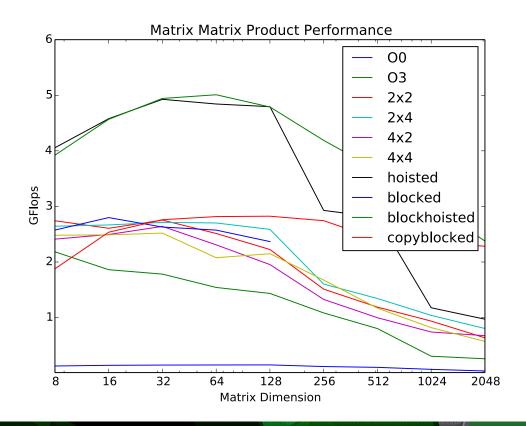

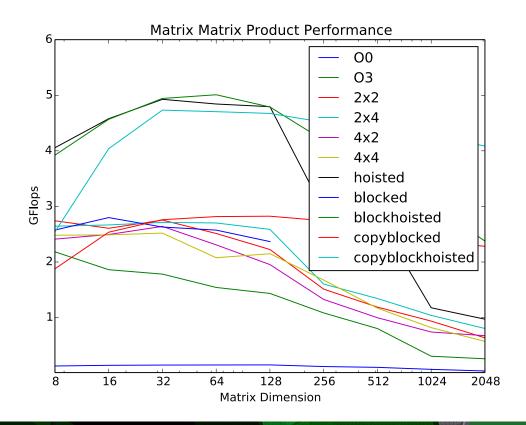

#### **Base Performance Results**

### Let's Make One Small Change

```

double benchmark(int M, int N, int K, long numruns) {

Matrix A(M, K), B(K, N), C(M, N);

Timer T;

T.start();

for (int i = 0; i < numruns; ++i) {

multiply(A, B, C);

}

T.stop();

bench: bench

c++ -03 -std

bench.o: ben

c++ -03 -std</pre>

```

Tell the compiler to use optimization level 3

```

bench: bench.o Matrix.o

c++ -03 -std=c++11 bench.o Matrix.o -o bench

bench.o: bench.cpp Matrix.hpp

c++ -03 -std=c++11 -c bench.cpp -o bench.o

Matrix.o: Matrix.cpp Matrix.hpp

c++ -03 -std=c++11 -c Matrix.cpp -o Matrix.o

```

#### **Base Performance Results**

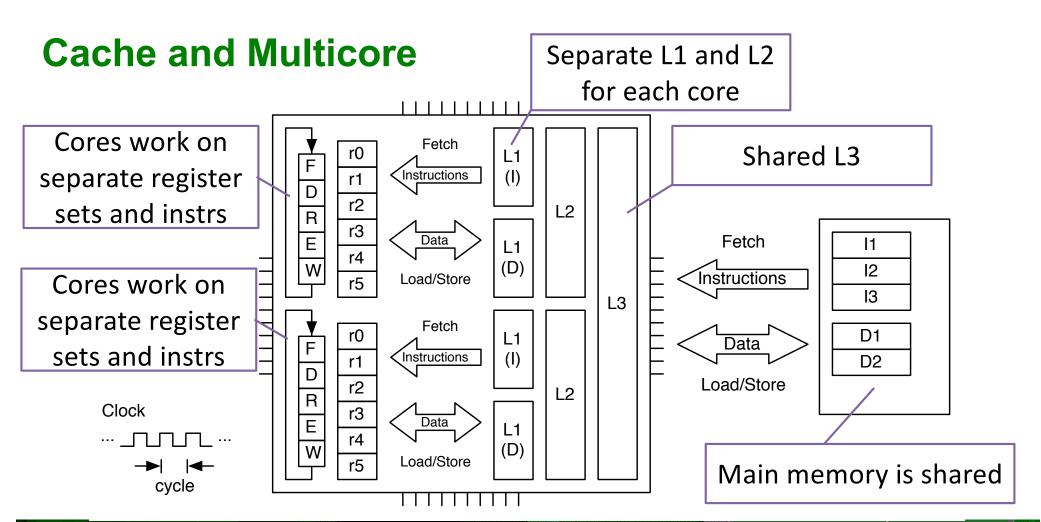

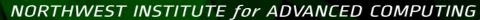

# The Three Most Important Requirements for HPC

- Locality

- Locality

- Locality

# **Locality -> Performance**

- Caches are much smaller than main memory. How do we decide what data to keep in cache to effect higher performance (more accesses)?

- Temporal Locality: if a program accesses a memory location, there

is a much higher than random probability that the same location will

be accessed again

- Cache replacement policies attempt to keep cached elements in the cache for as long as possible

- Spatial Locality: if a program accesses a memory location, there is a much higher than random probability that nearby locations will also be accessed (soon)

- Cache policies read contiguous chunks of data a referenced element and its neighbors – not just single elements

# **Improving Locality**

Consider each step of inner loop

- Load C(i,j) into register

- Load A(i,k) into register

- Load B(k,j) into register

- Multiply

- Add

- **Store**C(i,j)

reused?

- Four memory operations and two floating point operations per iteration

- 1/3 flop per cycle (if each operation is one cycle)

# **Improving Locality**

- Load C(i,j) into register

- Load A(i,k) into register

- Load B(k,j) into register

- Multiply

- Add

- Store C(i, j)

```

void multiply(const Matrix& A, const Matrix&B, Matrix&C) {

for (size_t i = 0; i < A.num_rows(); ++i) {

for (size_t j = 0; j < B.num_cols(); ++j) {

for (size_ k = 0; k < A.num_cols(); ++k) {

C(i,j) += A(i,k) * B(k,j);

}

}

}

What can be

reused?</pre>

```

- Four memory operations and two floating point operations per iteration

- 2/6 = 1/3 flop per cycle (if each operation is one cycle)

#### Hoisting

```

Hoist C(i,j)

```

- Load A(i,k)

- Load B(k, j)

- Multiply

- Add

```

void multiply(const Matrix& A, const Matrix&B, Matrix&C) {

for (size_t i = 0; i < A.num_rows(); ++i) {

for (size_t j = 0; j < B.num_cols(); ++j) {

double t = C(i,j);

for (size_t k = 0; k < A.num_cols(); ++k) {

t += A(i,k) * B(k,j);

}

C(i,j) = t;

}

}</pre>

```

- Two memory operations and two floating point operations per iteration

- 2/4 = 1/2 flop per cycle (if each operation is one cycle)

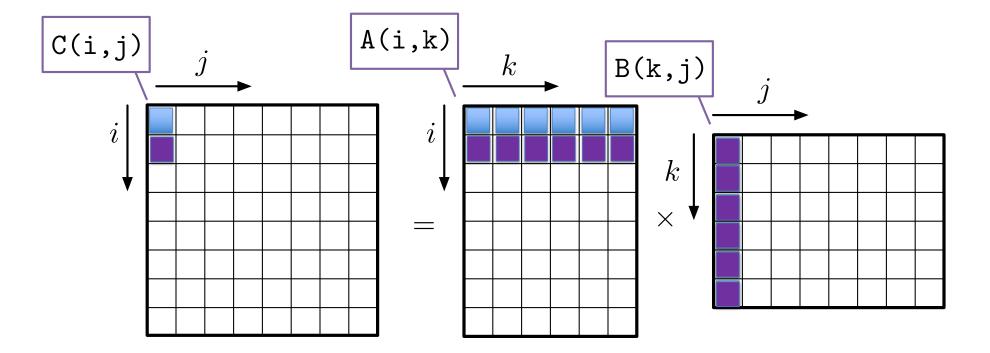

# **Order of Operations**

### **Order of Operations**

# Reuse: How Many Times Are Data Reused?

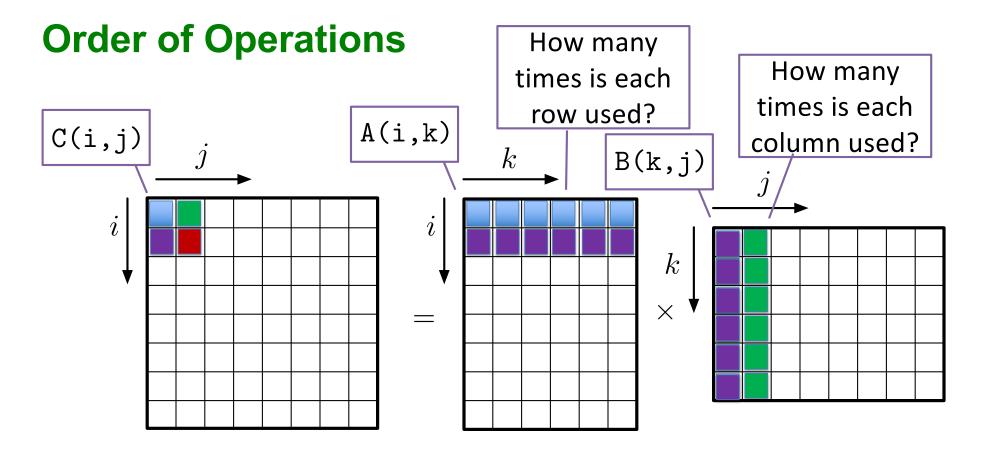

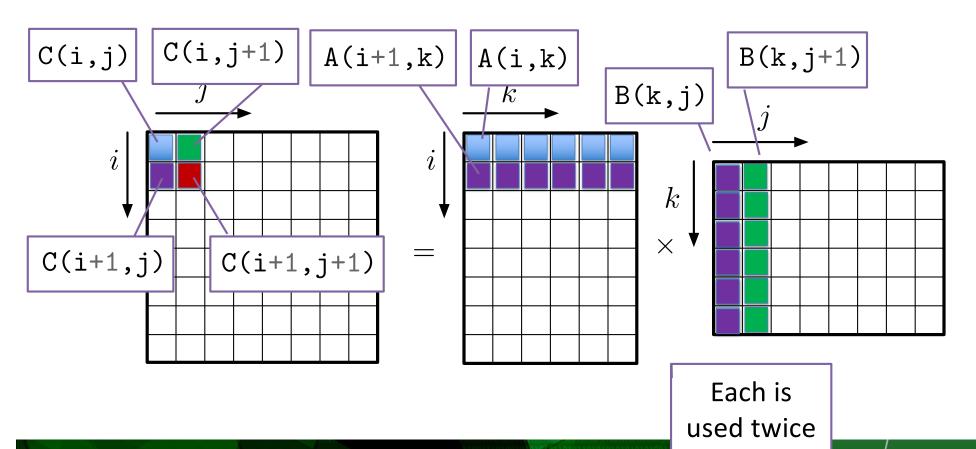

# Improving Locality: Unroll and Ja

```

B(k,j) is

used twice

void tiledMultiply2x2(const Matrix& A, const Matrix&B

for (size_t i = 0; i < A.num_rows(); i += 2) {

for (size_t j = 0; j < B.num_cols(); j += 2) {

for (size_t k = 0; k < A.num_cols(); +k) {

B(k,j+1) is

C(i, j) += A(i, k) * B(k, j);

used twice

C(i, j+1) += A(i, k) * B(k, j+1);

C(i+1, j) += A(i+1, k) * B(k, j);

C(i+1, j+1) += A(i+1, k) * B(k, j+1);

A(i,k) is

used twice

A(i+1,k) is

Can also hoist

(independent of k)

used twice

```

- Four memory operations and eight floating point operations per iteration

- 8/12 = 2/3 flop per cycle (if each operation is one cycle) 2X the base case

University of Washington by Andrew Lumsdaine

# **Example: Register Locality**

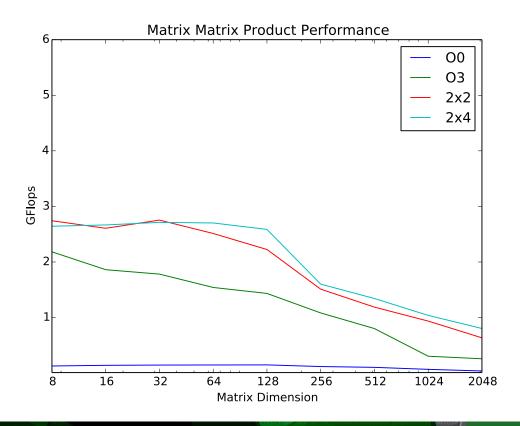

# 2 by 4

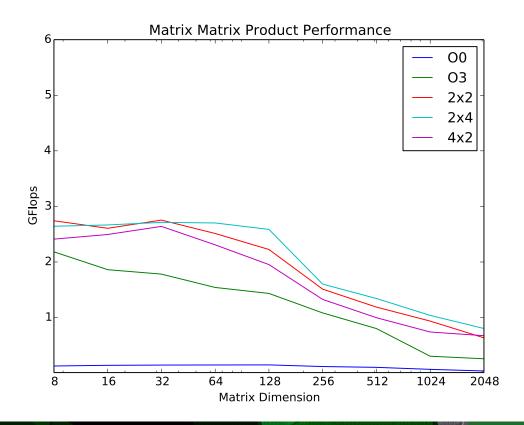

# 4 by 2

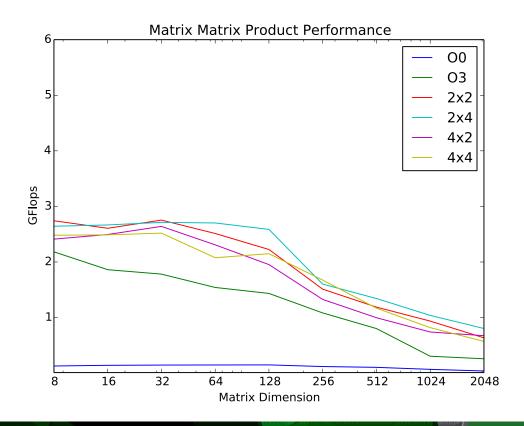

# 4 by 4

### **Tiling and Hoisting**

```

void hoistedTiledMultiply2x2(const Matrix& A, const Matrix&B, Matrix&C) {

for (size_t i = 0; i < A.num_rows(); i += 2) {

for (size_t j = 0; j < B.num_cols(); j += 2) {

double t00 = C(i, j); double t01 = C(i, j+1);

double t10 = C(i+1,j); double t11 = C(i+1,j+1);

for (size_t k = 0; k < A.num_cols(); ++k) {

t00 += A(i, k) * B(k, j);

t01 += A(i, k) * B(k, j+1);

Hoist 2x2 tile

t10 += A(i+1, k) * B(k, j);

t11 += A(i+1, k) * B(k, j+1);

C(i, j) = t00; C(i, j+1) = t01;

C(i+1,j) = t10; C(i+1,j+1) = t11;

```

NUKIHWESI INSIIIUIE JOT AUVANLEU LUMPUIING

# **Tiling and Hoisting**

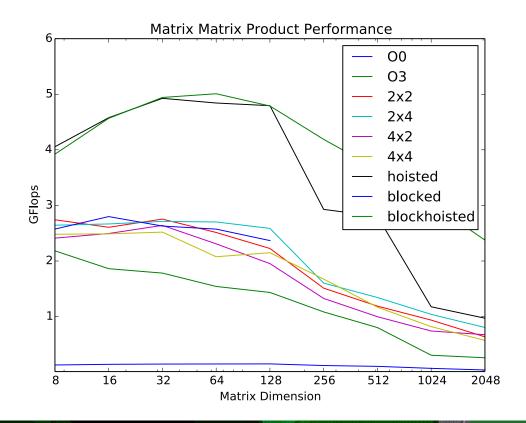

# **Improving Locality: Cache**

- Large matrix problems won't fit completely into cache

- Use blocked algorithm work with blocks that will fit into cache

$$C_{IJ} = \sum_{K} A_{IK} B_{KJ}$$

| $C_{00}$ | $C_{01}$ | $C_{02}$ | $C_{03}$ |

|----------|----------|----------|----------|

| $C_{10}$ | $C_{11}$ | $C_{12}$ | $C_{13}$ |

| $C_{20}$ | $C_{21}$ | $C_{22}$ | $C_{23}$ |

| $C_{30}$ | $C_{31}$ | $C_{32}$ | $C_{33}$ |

| $A_{00}$ | $A_{01}$ | $A_{02}$ | $A_{03}$ |

|----------|----------|----------|----------|

| $A_{10}$ | $A_{11}$ | $A_{12}$ | $A_{13}$ |

| $A_{20}$ | $A_{21}$ | $A_{22}$ | $A_{23}$ |

| $A_{30}$ | $A_{31}$ | $A_{32}$ | $A_{33}$ |

|   | $B_{00}$ | $B_{01}$ | $B_{02}$ | $B_{03}$ |

|---|----------|----------|----------|----------|

| × | $B_{10}$ | $B_{11}$ | $B_{12}$ | $B_{13}$ |

| ^ | $B_{20}$ | $B_{21}$ | $B_{22}$ | $B_{23}$ |

|   | $B_{30}$ | $B_{31}$ | $B_{32}$ | $B_{33}$ |

- Each product term fits completely into catherand runss at high performance

- Cache misses amortized

work with

data

#### **Blocking and Tiling**

```

void blockedTiledMultiply2x2(const Matrix& A, const Matrix&B, Matrix&C) {

const int blocksize = std::min(A.num_rows(), 32);

for (size_t ii = 0; ii < A.num_rows(); ii += blocksize) {</pre>

Outer loops work

for (size_t jj = 0; jj < B.num_cols(); jj += blocksize) {</pre>

for (size_t kk = 0; kk < A.num_cols(); kk += blocksize) {</pre>

across blocks

(for each block)

for (size_t i = ii; i < ii+blocksize; i += 2) {

for (size_t j = jj; j < jj+blocksize; j += 2) {</pre>

for (size t k = kk; k < kk+blocksize; ++k) {

C(i, j) += A(i, k) * B(k, j);

Inner loops

C(i, j+1) += A(i, k) * B(k, j+1);

work on blocks

C(i+1, j) += A(i+1, k) * B(k, j);

C(i+1, j+1) += A(i+1, k) * B(k, j+1);

```

# **Blocking and Tiling and Hoisting**

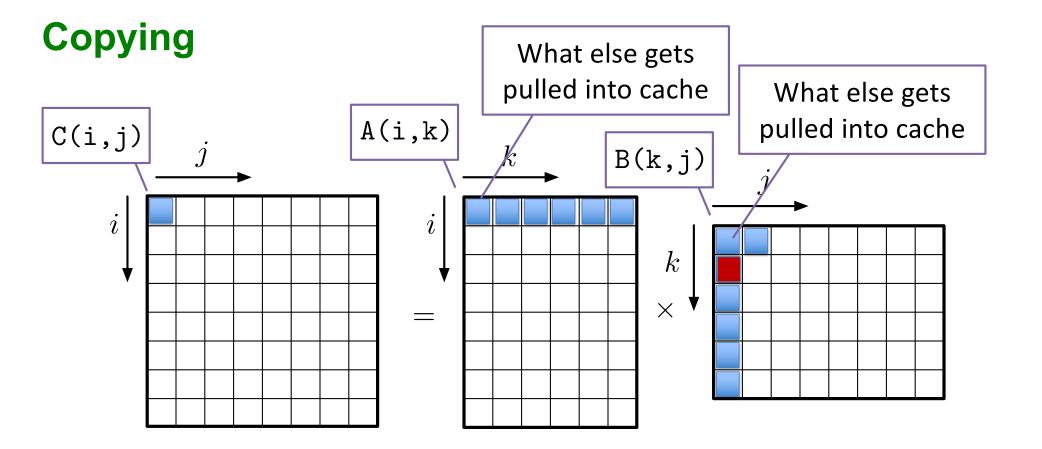

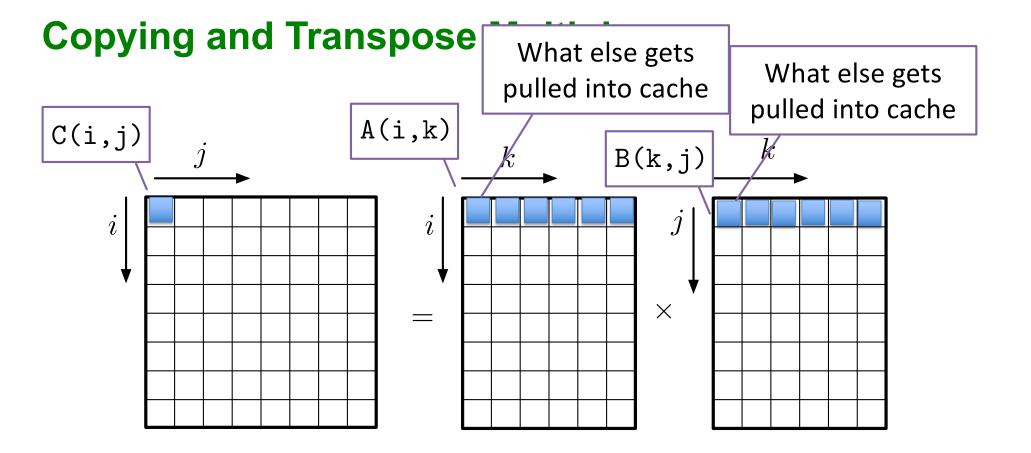

# **Copying and Blocking and Tiling**

# **Blocking and Tiling and Hoisting and Copying**

#### Recap

- Locality: Write software so hardware can leverage it

- Register locality (tiling / unroll and jam)

- Hoisting

- Blocking

- Copying / transpose multiply

- Always use –O3 for release (not for debug)

#### **Name This Famous Person**

Any sufficiently advanced technology is indistinguishable from magic

### This Nearly Famous Person Says

Optimizing compilers are sufficiently advanced technology

And so are modern microprocessors

But especially optimizing compilers for modern microprocessors

Magic: the power of apparently influencing the course of events by using mysterious or supernatural forces

# **Tuning**

Starting with base code

Various compiler optimizations help

- Tiling (which size)

- Blocking (what size)

- What size works best for Tiling and Blocking together?

- What loop ordering? Matrix matrix product has six different orderings? What block ordering?

- What about when we add AVX, and threads, etc?

Magic: the power of apparently influencing the course of events by using mysterious or supernatural forces

The answer will be different for different CPUs

How do we find

the optimal

combination?

# **Finding the Sweet Spot**

- Exhaustive parameter space search

- Tiling, Blocking, Compiler flags, AVX inst, loop ordering

- Original project at UC Berkeley phiPAC (Bilmes et al)

- Further developed by Whaley and Dongarra → Automatically Tuned Linear Algebra Subprograms (ATLAS)

- Recently honored with "test of time" award

This started as a final course project

The competition was to write fastest matrix-matrix product

Students were the good kind of lazy

And wrote a program

to generate different

multiply functions

# Thank you!

© Andrew Lumsdaine, 2017-2018

Except where otherwise noted, this work is licensed under

https://creativecommons.org/licenses/by-nc-sa/4.0/

#### **Microprocessors**

Basic operation: read and execute program instructions stored in memory

Fundamental performance / efficiency metric: cycles per instruction (CPI) also FL( Instructions can only be Fetch run in CPU Instructions **Transitions CPU** Memory Clock move data Data through CPU Program Load/Store cycle Data can only instructions be operated and data on in CPU NORTHWEST INSTITUTE for ADVANCED CUMPUTING

#### **Processor Core Instruction Handling**

A single instruction may require multiple steps from fetch to

completion

# **Processor Core Instruction Handling**

By pipelining, multiple instructions can be executed at each clock

cycle Fourth is Form of instruction-level parallelism fetched Fetch 11 **Fetch** 14 12 Instructions 13 13 Decode R Read 12 D<sub>1</sub> Data 11 Execute Clock D2 R Write Load/Store Previous cycle instructions move along